**SAMSUNG**

| All information in this specification are subject to change without notice for product |

|----------------------------------------------------------------------------------------|

| improvement. The information, circuits and all other data included herein are believed |

| to be accurate and reliable.                                                           |

However, no responsibility is assumed by SAMSUNG for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

1989

by

SAMSUNG

# **TABLE of CONTENTS**

| CHAPTER   | ı  | INTRODUCTION 7                                                   |

|-----------|----|------------------------------------------------------------------|

|           |    | 1.1 General                                                      |

|           |    | 1.2 Policy                                                       |

|           |    | 1.3 Scope                                                        |

| CHAPTER   | II | QUALITY MANAGEMENT and ORGANIZATION9                             |

|           |    | 2.1 General                                                      |

|           |    | 2.2 Policy                                                       |

|           |    | 2.3 Scope                                                        |

|           |    | 2.4 Quality Department Organization                              |

|           |    | 2.5 Quality and Reliability Function Procedure                   |

|           |    | 2.6 Education and Training                                       |

| CHAPTER I | Ш  | PROCESS CONTROL PROGRAM13                                        |

|           |    | 3.1 Process Control Policy                                       |

|           |    | 3.2 Process Control Methods                                      |

|           |    | 3.3 Data Reporting                                               |

|           |    | 3.4 Corrective Action                                            |

|           |    | 3.5 General Process Control                                      |

|           |    | 3.6 Wafer Fabrication (Raw material incoming inspection)         |

|           |    | 3.7 Process Control-Assembly 3.8 Material Control                |

|           |    | 3.8 Material Control 3.9 Vendor Relations                        |

|           |    | 3.10 Control of Finished Product                                 |

|           |    | 3.11 Inspection Control                                          |

|           |    | 3.12 Calibration                                                 |

| CHAPTER I | ٧  | QUALITY ASSURANCE and RELIABILITY PROGRAM $\dots 43$             |

|           |    | 4.1 Introduction                                                 |

|           |    | 4.2 Policy                                                       |

|           |    | 4.3 Scope                                                        |

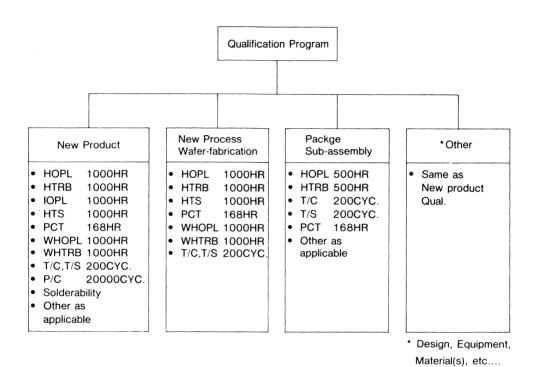

|           |    | 4.4 Qualification Procedure                                      |

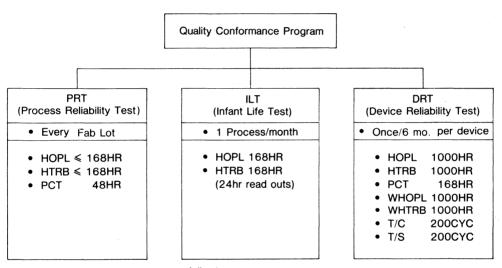

|           |    | 4.5 Product Reliability (Quality Conformance) Monitors           |

|           |    | 4.6 Reliability Tests                                            |

|           |    | 4.7 Relative Stress Comparisons                                  |

|           |    | 4.8 Reliability Test Results 4.9 Product Outgoing Quality Levels |

|           |    | 4.5 Froduct Odtgoing Quality Levels                              |

# **TABLE of CONTENTS (continued)**

| CHAPTER   | ٧        | DOCUMENT CONTROL SYSTEM59                            |

|-----------|----------|------------------------------------------------------|

|           |          | 5.1 Introduction                                     |

|           |          | 5.2 Policy                                           |

|           |          | 5.3 Scope                                            |

|           |          | 5.4 Document Flow                                    |

| CHAPTER   | VI       | CUSTOMER RETURNS61                                   |

|           |          | 6.1 General                                          |

|           |          | 6.2 Route and Action                                 |

|           |          | 6.3 Customer Return Procedure                        |

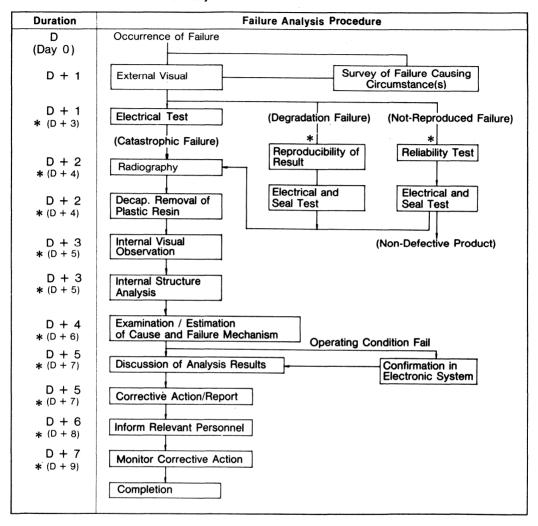

| CHAPTER V | <b>/</b> | FAILURE ANALYSIS63                                   |

|           |          | 7.1 Introduction                                     |

|           |          | 7.2 Policy                                           |

|           |          | 7.3 Scope                                            |

|           |          | 7.4 Procedure                                        |

|           |          | 7.5 Failure Modes and Mechanisms                     |

|           |          | 7.6 Equipment                                        |

|           |          | 7:7 General Customer                                 |

|           |          | 7.8 Customer Return Analysis                         |

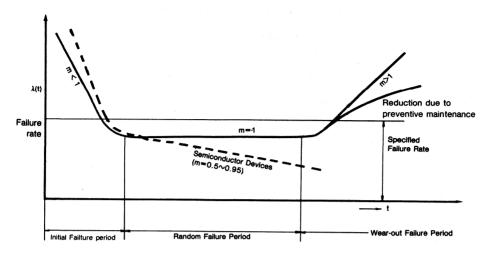

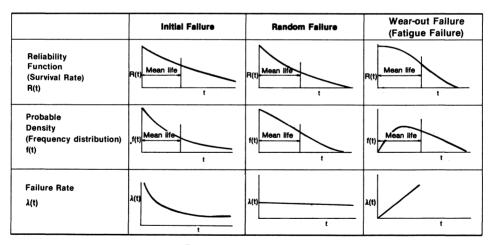

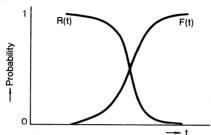

| APPENDIX: | RI       | ELIABILITY and PREDICTION THEORY81                   |

|           | 1.       | Reliability of Semiconductor Devices                 |

|           | 2.       | Accelerated Reliability Testing                      |

|           | 3.       | Use of Semiconductor Devices to Maintain Reliability |

## INTRODUCTION

### CHAPTER I INTRODUCTION

### 1.1 General

This manual establishes the basic philosophies and procedures of quality programs implemented by Samsung Semiconductor and Telecommunication Ltd. A clear focus on the critical nature of reliability and quality makes Samsung a leader in semiconductor product assurance.

Samsung has been providing a wide variety of semiconductor products to the world for many years. Extensive inroads and insights have been used to create methods which most effectively result in reliable products. As a developer and user of Statistical Process Control curricula, Samsung pays strict attention to manufacturing reproducibility. Long ago realizing the key to enhanced reliability was process control, stringent statistical analysis has been instituted by Samsung for many years.

Fully described within this manual are the quality assurance procedures which Samsung carries out to guarantee the integrity of its products. Items detailed include general standards, tests performed and test results, process and document control, assurance operations, customer support, and failure analysis methodologies.

### 1.2 Policy

Samsung's semiconductor division management philosophy is to manufacture a product commensurate with corporate policy and customer contract requirements. Samsung sets its standards to exceed those of the most rigorous consumers, such that any customer will receive only completely qualified product.

It is the responsibility of the reliability and quality department to assure that these requirements are met.

### 1.3 Scope

The policies discussed above have been established to provide a quality program in the areas of design, development, production, inspection, and test for semiconductor products.

In the event of any inconsistency between this document and specific contractural requirements and schedules, the contract requirements and schedules will take precedence.

## QUALITY MANAGEMENT and ORGANIZATION

### CHAPTER II QUALITY MANAGEMENT and ORGANIZATION

### 2.1 General

Samsung has adopted a TOTAL QUALITY CONTROL approach, which means that everybody in the company contributes to quality improvement. Such an approach can solve quality problems at the stage where they arise, so that latent failures are not carried over to the next stage, or to finished goods. TOTAL QUALITY CONTROL assures the prevention of quality problems, rather than simply eliminating defective finished products. Naturally the customer benefits from the approach, as it quarantees very strong quality and reliability. As a consequence, costs to the customer for their finished products are reduced.

### 2.2 Policy

It is the company's policy that all products shall be efficiently and economically manufactured in compliance with uniformly high standards of quality. The quality department has full responsibility for establishing and implementing any procedures necessary to ensure this policy.

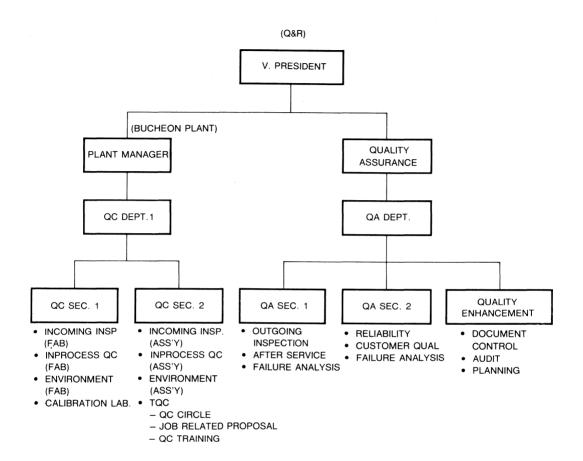

The organization of the company ensures that the quality function will at all times have the authority to carry out this policy. As Fig. 1 demonstrates, quality assurance reports directly to the presidential level, while quality control also reports to an upper management level.

### 2.3 Scope

The quality organization sets quality control and reliability targets for all products, defines procedures and the specification system, and regularly audits their implementation. Application is to all manufacturing stages, and includes heavy interfacing with development and production personnel. The quality group is also responsible for the evaluation of new processes, the development of advanced failure analysis techniques, reliability prediction, and advanced reliability studies utilizing novel techniques. When a customer requires additional quality controls or special reliability procedures for product, the quality department ensures compliance to the particular specifications.

### 2.4 Quality Department Organization

Figure 1 delineates the differing sections and their functions within the quality organization. Both quality control and quality assurance are detailed.

### 2.5 Quality and Reliability Function Procedure

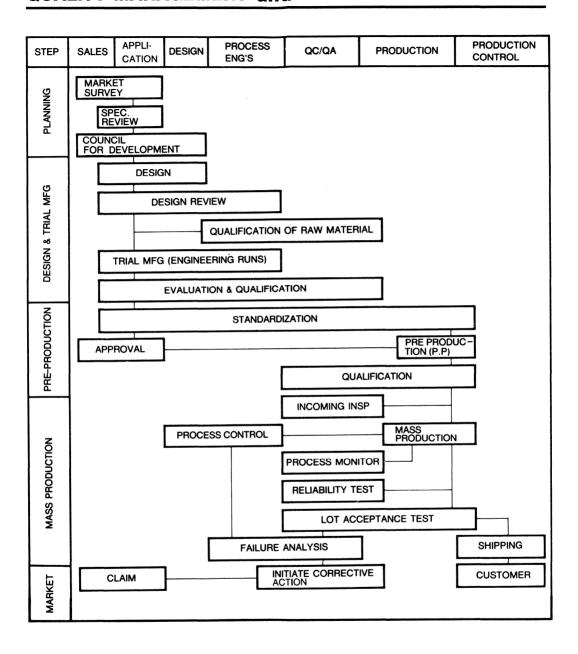

From development to customer after-sales service, the product assurance system is outlined in Figure 2. Qualification testing for new products, significance testing for engineering changes, in-process quality controls, batch acceptance testing, periodical reliability testing, and customer service are all performed under a unified system.

### 2.6 Education and Training

Management at Samsung has always given top priority to quality. For this reason, the quality department has organized a quality training program. Training seminars, sometimes with external consultant's support, are run at all levels. This starts from upper management, and includes engineers, quality personnel, production supervisors, and workers. The objective of the training seminars is to improve quality and reliability, to reduce costs by eliminating rejects, to promote greater awareness of the importance of quality, and to encourage participation in the solution of quality-related problems.

# **QUALITY MANAGEMENT AND ORGANIZATION**

Fig. 1. Quality control organization chart

# **QUALITY MANAGEMENT and ORGANIZATION**

Fig. 2. Quality and reliability function procedures

### CHAPTER III PROCESS CONTROL PROGRAM

### 3.1 Process Control Policy

The policy of the company on process control is as detailed below.

- 3.1.1. Any operation, test, or measurement used in manufacturing must be formally specified. The approval of a quality engineer is required for all specifications relating to purchased items, along with all specifications relating to the manufacture and testing of standard and custom products.

- 3.1.2 Purchased materials and piece parts must be ordered to a formal specification from an approved supplier. Purchased items must be checked against the purchase specification and accepted by the quality department before being used.

- 3.1.3 The manufacturing department is responsible for performing operations and processes in accordance with specifications, and for the manufacturing quality of the product. The quality function, in particular quality control, is required to ensure that specified methods are used, and that specified quality standards are maintained by the methods listed in the following sections.

### 3.2 Process Control Methods

The quality control department assures compliance with the above policy by:

- 3.2.1. Auditing processing methods.

- 3.2.2 Performing in-process and finished product monitoring.

- 3.2.3 Providing information for, and assuring completion of, corrective action.

- 3.2.4 Providing criteria for (and means of) identifying acceptable and defective product.

- 3.2.5 Conducting monitor control in conformity with processing and fabrication specifications.

### 3.3 Data Reporting

- 3.3.1 Process control data is recorded on an attribute basis or form as required, with control charts maintained on a regular basis. This data is reviewed periodically and serves as the basis for judging the acceptability of specific processes.

- 3.3.2 Inspection reporting

The result of each inspection, confirmed by operator and inspector, is recorded on a quality control form and/or computer. Defective work is reported immediately to production supervisors, in major cases using an in-process rejection form designed to convey the relevant data. A copy of every inspection result is submitted to the chief inspector.

3.3.3 Summaries of results

The results of inspection, normally summarized on a weekly basis, are presented on summary forms. The results may be compared with historical data, so that the trends for overall quality can be seen. Summary data from the various process control operations are relayed to cognizant line, engineering, and management personnel in real time. Thus, if appropriate, corrective actions can be taken immediately.

### 3.4 Corrective Action

#### 3.4.1 General

Checks are made throughout the receiving, manufacturing and test operations to identify existing or potential deficiencies in company products. When these checks indicate conditions which may result in substandard or defective material, preventative actions are undertaken. In addition, customer feedback data, along with requests for failure analysis and corrective action, are a part of the actual checking system.

3.4.2 Corrective action procedure

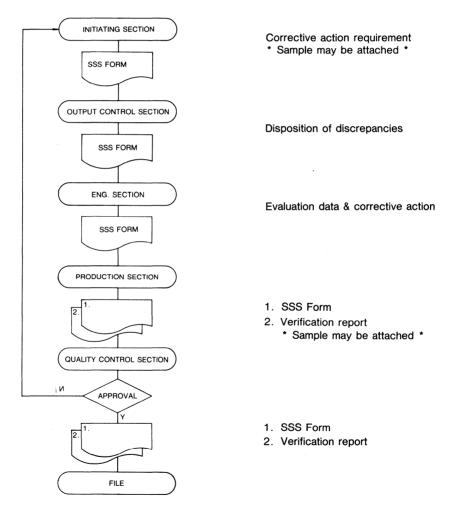

There are three formal levels of corrective action which may be taken under the corrective action procedure shown in Fig. 3.

- Following the failure of an in-line or batch acceptance sample at a quality control or production inspection, action is taken by production to screen, rework, or scrap the defective lot. To prevent a re-occurence of the fault, any necessary action is undertaken.

- 2) If action at the first level is ineffective, or if the fault persists, a quality engineer describes the status of the failure on appropriate documentation. This is then directed to the production engineer in charge and to the manager of the area concerned. The engineer is required to take corrective action immediately. The quality control engineer monitors the adequacy of this action, to ensure the problem is being addressed properly. If corrective action is neither taken nor effective, the next higher level of management is involved in the matter until the problem in question is solved.

- If quality is directly affected, a work stoppage may be enforced to prevent further production of defective material.

Fig. 3. Corrective action procedure

#### 3.5 General Process Control

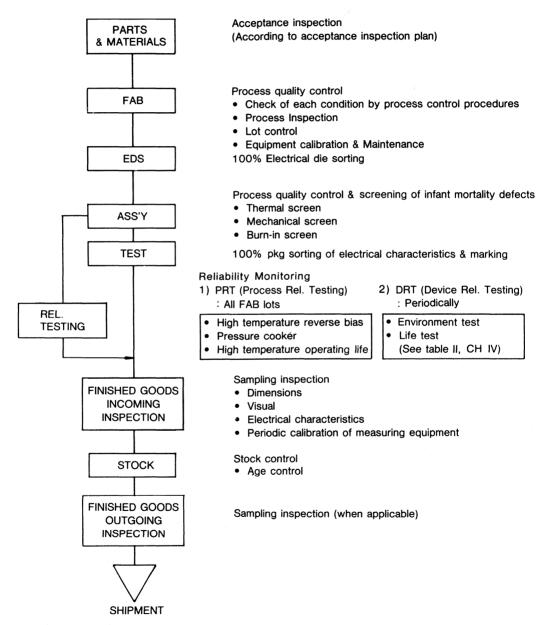

Samsung's general process flow is shown in Fig 4.

This illustration contains the standard process flow from incoming parts & materials to customer shipment.

Fig. 4. General process flow chart

### 3.6 Wafer Fabrication (Raw material incoming inspection)

Samsung itself manufactures few materials used for wafer fabrication. Silicon, chemicals, and other materials are all purchased from Samsung-qualified and-approved vendors.

To ensure that only materials of the highest quality are used. Samsung has an evaluation system (program) for vendor quality improvement.

This evalution system operates under the following policies:

- Establish technical relationships with Samsung's selected vendors to mutually improve the entire technology.

- Improve product quality through mutual interaction to achieve low defect levels. In this way, Samsung incoming inspection becomes a data-gathering activity.

- This program is manifested in a vendor quality evaluation report, in which vendors measure product quality to Samsung specifications, and Samsung accepts product based on vendor-supplied data.

- Base purchase allocations are made on quantitative vendor comparisons, where quality, delivery, total

cost, and vendor responsiveness to Samsung are considered in determining each vendor's ranking

and rating.

- 3.6.1. Wafer inspection

Inspection procedures are based on three categories:

- 1. Visual inspection

- 2. Dimensional inspection

- 3. Material property measurement

During inspection, discrepant lots are occasionally encountered. The disposition of discrepant material is to normally return it to the vendor. However, if the material is deemed as suitable for use, there are many possible resultant actions:

- 1. 100% screen the incoming material to physically remove defective items.

- Modify the Samsung specification if it is discovered through reject analysis the specification is improper.

- 3. QC actions are all documented and have lead to vendor or internal corrective actions.

Table I lists the silicon wafer inspection techniques used at Samsung.

### (Table I) Silicon Wafer Inspection techniques

| Purpose                                     | Instruments                       | Sample         |

|---------------------------------------------|-----------------------------------|----------------|

| Structural                                  | — Secco Etch                      | All Lots       |

| <ul> <li>Crystallographic Defect</li> </ul> | - Sirtl Etch (Microscope)         | (Small Sample) |

| Electrical                                  |                                   |                |

| - Resistivity                               | - Kokusai VR-30A                  |                |

|                                             | (4 Point Probe)                   |                |

| <ul> <li>Conductivity type</li> </ul>       | Tencor Sonogage                   | All Lots       |

|                                             | — ASM AFPP                        |                |

|                                             | - Mercury Probe (811)             |                |

|                                             | (MDC CSM System)                  |                |

|                                             | — Tencor Ten-Type                 |                |

| Dimensional                                 | - Non-Contact Thickness Gage      |                |

| - Thickness                                 | (ADE6034)                         |                |

| - Diameter                                  | - EPI-Layer Thickness Gauge       | All Lots       |

|                                             | (Digilab FTG-12)                  |                |

| - Orientation                               | - Qualimatic S-100                |                |

| - Flatness (TIR)                            | - Flatness Measuring System       |                |

|                                             | (Siltec)                          |                |

| Visual                                      | Automatic wafer Inspection System |                |

| - Surface Quality                           | (Aeronca WIS-150)                 | All Lots       |

| - Cleanliness                               | - Unaided Eye                     | All Lots       |

### 3.6.2 Mask Inspection

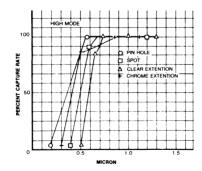

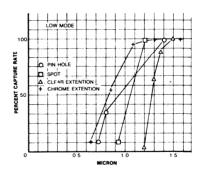

Mask parameters and tolerances are established by design and development engineers. Samsung utilizes state-of-the-art automatic inspection instrumentation with guaranteed repeatability. Recent results demonstrate nearly zero defects greater than 0.7um in the case of the incoming masks. Samsung reinspects photoplate masks after every 10 times of use as part of it's preventative maintenance procedures. Table II lists the mask inspection technology currently used as Samsung.

(Table II) Mask Inspection Technology

| Purpose                                                                                                                                          | Instrument                                       | Sample                          | Criteria                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------|---------------------------------------------------|

| Defect Detection     Pin Hole & Clear-Extension     Opaque Projection & Spots     Scratch/Partice/Stain     Substrate Crack/Glass-Chip     Other | NJS 5MD – 44<br>(Auto Mask<br>Inspection System) | All Masks                       | ≤ 1.5 um Defects     ≤ 0.124 ea/cm Defect Density |

| Registration Run-Out (X-Y Coordinate) Orthogonality Drop-in Accuracy Die Fit/Rotation                                                            | MVG 7×7 Comparator                               | 20%<br>All<br>New Masks<br>100% | ~ 0.5 um<br>Defects                               |

| Critical Dimension                                                                                                                               | MPV-CD 1,2 Automatic Line Width Measuring System | All Masks                       | Purchasing Spec.                                  |

### \* Mask Defect Capture Rate (Graph)

### 3.6.3 Chemical inspection

Examples of relevant chemicals are photo resists, developers, solvents, acids, and dopants. Chemical composition and related characteristics aren't normally subject to a physical incoming inspection. Samsung receives the certification card and/or outgoing inspection result of a particular vendor and judges for proper quality. Examination consists of, but is not limited to: proper composition, proper concentration, and expiration date.

The chemical container, which must be free from any contamination, must be quality assured at incoming inspection. Naturally materials and their properties are monitored during production to assure that quality is maintained.

#### 3.6.4 Wafer Fabrication

### 3.6.4.1 Process control

Quality programs utilize the following methods of control to achieve previously stated objectives: process audits, environmental monitors, lot acceptance inspections, and process integrity audits. A general wafer fabrication flow is shown in Fig. 6.

#### 3.6.4.2 Definitions

Essential components of the quality control program are defined as follows:

- 1) Process audit -performed quarterly on all operations critical to product quality and reliability.

- Environment monitor monitors concerning the process environment. Examples include water purity, temperature, humidity and particle counts.

- 3) Process monitor periodic inspections at designated process steps to verify manufacturing inspections and maintenance of process averages. These inspections provide both attribute and variable data.

- 4) Lot acceptance lot by lot sampling. This sampling method is reserved for those operations deemed as critical and, as such, require special attention.

#### 3.6.4.3 Environmental monitor

### (Table III Environment Monitoring Item)

| Process    | Control item                          | Spec. Limit       | Insp. Frequency |

|------------|---------------------------------------|-------------------|-----------------|

| Clean room | Temperature                           | Individual spec.  | 1 HR            |

|            | Humidity                              | . "               | 1 HR            |

|            | <ul> <li>Partićle (≥0.3um)</li> </ul> | ,,                | 1 HR            |

|            | Air velocity                          | ,,                | 1 HR            |

| D.I Water  | Particle                              |                   |                 |

|            | - Main                                | • < 4 ea / 1 ml   | 1 HR            |

|            | <ul> <li>Using point</li> </ul>       | • < 7 ea / 1 mi   |                 |

|            | Bacteria                              |                   |                 |

|            | – Main                                | 50 Colonies/100ml | Weekly          |

|            | <ul> <li>Using point</li> </ul>       | (0.45um)          | Monthly         |

|            | Resistivity                           |                   |                 |

|            | - Main                                | • ≥ 16 Mohm-cm    | 1 HR            |

|            | Using point                           | • ≥ 14 Mohm-cm    | 24 HR           |

|            | Silica count                          | • < 20 PPB        | 24 HR           |

#### \* Instruments

- FMS (Facility monitoring system) HIAC/ROYCO

- CPM (Central particle monitoring system) Dan Scientific

- · Liquid dust counter

- · Filtration system for bacterial check

- Air particle counter

- · Air velocity meter

## 3.6.4.4 Process controls and monitors

A Basic listing of process controls and monitors is presented in Table IV.

Table IV Process and equipment controls in wafer fab

| Process step<br>or equipment | Measured attribute                                                                                                  | MFG. Inspection                     | Process control(QC) inspection    |

|------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------|

| Facilities                   | - Particle counts - Temperature - Humidity                                                                          | <br><br>                            | YES<br>YES<br>YES                 |

|                              | DI Water     Machine pm's     Equipment calibration                                                                 | <br>YES<br>YES                      | YES<br>YES<br>YES                 |

| Photo                        | - Critical dimensions(CDs) - Alignment - Resist thickness - Particles - Visual Insp - Develop check                 | YES YES YES YES YES YES             | YES YES YES YES                   |

| Etch                         | Mask visual and defect inspection  Power levels                                                                     | YES                                 | YES                               |

| Etcii                        | - Fower levels - Temperature - Gas flows - Etch rates - Selectivity - Etch Insp - Final Insp - Defects              | YES YES YES YES YES YES YES YES YES | <br><br><br><br>YES<br>YES        |

| Oxidation                    | - Temperature - Temperature profile - Gas flows - C/V monitors - V/I monitors - Film thickness - Visuals - Particle | YES YES YES YES YES YES YES YES YES | -<br>-<br>-<br>-<br>-<br>YES<br>- |

| Ion implant                  | <ul><li>V/I monitors</li><li>C/V monitors</li><li>E-test</li></ul>                                                  | YES<br>YES<br>YES                   | -<br>-<br>-                       |

| Metallization                | <ul><li>Thickness</li><li>Reflectivity</li><li>Step coverfage</li><li>Electromigration</li></ul>                    | YES<br>YES<br>—                     | -<br>YES<br>YES                   |

| CVD                          | <ul><li>Thickness</li><li>Wt% of PSG</li><li>Refractive index</li><li>Stress</li></ul>                              | YES<br>YES<br>YES                   | YES<br>YES<br>YES<br>YES          |

| Wafer back-<br>side prep.    | Wafer thickness & finish     Back side metal resistivity                                                            | YES<br>YES                          | YES<br>—                          |

| Outgoing                     | <ul><li>– 100X MFG. Visual</li><li>– 100X QC outgoing visual</li></ul>                                              | YES —                               | —<br>YES                          |

Note: Where inspection is peformed, it is normally done once per each work shift. MFG. represents Manufacturing

### 3.6.4.4.1 Photo/Etch process control

Figure 5. schematically illustrates the process steps in a typical photo/etch operation. Each step is carefully monitored for proper equipment settings, preventive maintenance, and calibration. The final thickness and integrity of the photoresist layer are measured and inspected by QC. After develop, "Develop Check" inspection verifies proper exposure and critical dimensions (CDs).

The subsequent ion implant and/or etch operation is performed and the photoresist removed by wet or plasma etch techniques.

"Final Check" is performed by QC on every lot to verify the final CDs are correct and material removal is complete. Possible un/over etch, residual photoresist and masking defect (mask, expose, or photoresist-related) are also checked.

Fig 5. Control items in photo/etch process.

| Process Flow          | Process Step        | MFG. Control Item                                                                                   | QC Monitor/Gate                                                               |

|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| <b></b>               | Prebake             | Oven PM, Temperature,<br>Time, N2 Flow Rate                                                         |                                                                               |

|                       | Photoresist  - Spin | Machine PM                                                                                          | Thickness, Pinhole                                                            |

|                       | Soft Bake           | Oven PM, Temperature, Time                                                                          |                                                                               |

|                       | Align/Expose        | Light Uniformity Alignment, Focus Test, Mask Clean Inspection, Mask Clean Exposure, Light Intensity |                                                                               |

|                       | Develop             | Equipment PM<br>Solution Control                                                                    |                                                                               |

|                       | Develop<br>Check    | Photoresist Critical Dimensions, Particles, Mask and Resist Defects                                 |                                                                               |

| $\langle \rangle$     | QC Inspection       |                                                                                                     | Critical Dimension                                                            |

| A                     | Hard Bake           | Oven PM, Temperature,<br>Time, N2 Flow Rate                                                         |                                                                               |

|                       | Etch                | Equipment, PM & Settings,<br>Etch Time To Clean                                                     | Etch Rate                                                                     |

|                       | Over/Under          |                                                                                                     |                                                                               |

| $\overline{\bigcirc}$ | Photoresist         | Machine-PM                                                                                          |                                                                               |

|                       | Final Check         | CD's, Over and Under Etch, Particles, Photoresist Residue, Defects, Scratches                       |                                                                               |

|                       | QC Inspection       |                                                                                                     | Same as Final Check. However, more Intense on Limited Sample Basis (AQL 4.0%) |

Note: PM represents preventive maintenance

### 3.6.4.4.2 Gate oxidation process control

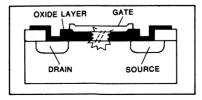

Gate oxide integrity is obviously of prime concern to the reliability of MOS device. The preclean step consisting of an acid dip followed by a series of rinses is carefully monitored for acid strength, DI water cleanliness and spin-rinse dryer operation.

Particle counts are taken at all steps of the oxidation process.

Furnace preventive maintenance is performed per a rigid schedule.

This includes temperature profiles and C/V monitors sensitive to contamination.

Fig6. illustrates the process flow at this step.

Final gate oxide thickness are measured on every run, and trended on statistical control charts with warning and actual process shut down limits.

Final gate oxide thickness measurement equipment is calibrated and checked routinely. Further down stream in the process, after metallization is in place, there are specific electrical tests performed on test structures to evaluate oxide properties and defect densities.

Oxide integrity is also evaluated at Wafer Sort where special electical stressing, designed to cause fallout on falut product, is performed.

|                      | MFG. & QC checks                                                                               |

|----------------------|------------------------------------------------------------------------------------------------|

| preclean             | etch rate, equipment PM,<br>D.I water purity, particle counts                                  |

| oxidation            | furnace PM, temperature profile, C/V monitors, furnace setting, push-pull rates, water loading |

| thickness<br>measure | thickness measurement, particle counts, measuring equipment calibration                        |

Fig. 6. Gate oxidation process flow.

### 3.6.4.4.3 Reliability-related interlayer Dielectric, Metallization, and Passivation process control.

Issues specific to reliability which are carefully monitored in cooperation with the wafer Fab Reliability group are:

Weight percent phosphorus content of the dielectric glass

Metallization integrity/defect density

Al step coverage

Passivation thickness and step coverage

Film stress

Passivation pin hole

Residual resistance in the metallization process

Electromigration

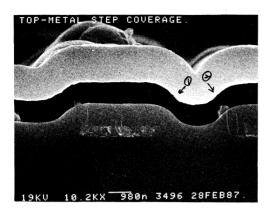

The Fab QC publishes Q&R monitor reports for Fab critical parameters on a weekly or monthly basis. A phosphosilicate glass wt.% P control chart is drawn on line. Following picture show a typical AI step coverage measurement performed by Fab. QC.

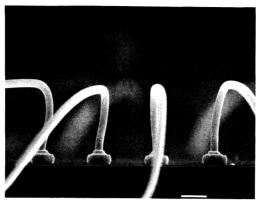

Al step coverage monitor performed by QC/QA

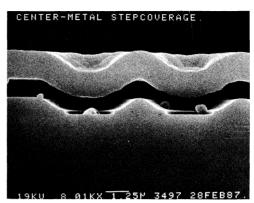

Both passivation thickness and metal etching profile for passivation step coverage are monitored on a weekly basis by Fab. QC.

Following picture show the passivation thickness and metal etching profile.

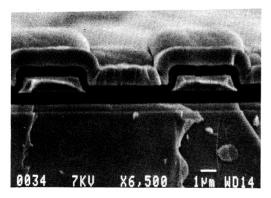

(a) Metal wet etching

(b) Metal Dry etching and Ashing.

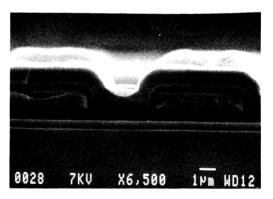

Following picture shows Metal surface/top side view.

The Reduction of an effective metal line cross-sectional area is monitored for the process with Nitride passivation layers. Both reduction of an effective metal line cross-sectional area and difect density data are regularly trended.

The Reduction of an effective metal line cross-sectional avea.

Passivation pin hole, Film stress, Electronigration, and Residual Resistance (in the metallization process) data are simillarly trended.

MOS process cross section/Junction profile.

SEM micrographs of transfer cross-sections in the following picture illustrate the effective channel length and the LDD (Lightly doped drain) which has occurred in qualifying of HMOS products.

### 3.6.4.4.4 Process audit (check)

### 1) Equipment checks

The manufacturing & QC sections have the responsibility for regular equipment checks which verify that operations are being run within specified settings and parameters. The Q.C section also assures that necessary preventive maintenance procedures have been performed on schedule, and that the equipment is in calibration.

### 2) Proces control item check

Important process control items must be specified on control charts prepared by the manufacturing section. QC audits these control charts regularly and verifies corrective actions for out of spec. and/or control limit issues.

### 3.6.4.4.5 Manufacturing equipment qualification

Q.C has the responsibility for manufacturing equipment qualification. This applies to not only manufacturing equipment for wafer production, but also new manufacturing equipment.

Fig. 6. General wafer fabrication flow

| Process Flow | Process Step               | Major Control Item             |

|--------------|----------------------------|--------------------------------|

|              | Wafer and Mask Input       |                                |

|              | Starting Material          | Wafer(See 3.6.1)               |

|              | Incoming Inspection        | Mask (See 3.6.2)               |

|              | Wafer Sorting and Labeling | Resistivity                    |

|              | Initial Oxidation          | Oxide Thickness                |

|              | Photo                      | See 3.6.4.4.1                  |

|              | Inspection                 | Critical Dimension             |

|              |                            | Visual/Mech AQL 4.0%           |

|              | QC Gate                    | Critical Dimension             |

|              | Etch                       | See 3.6.4.4.1                  |

|              | Inspection                 | Critical Dimension             |

|              |                            | Visual/Mech AQL 4.0%           |

|              | QC Gate                    | Critical Dimension Visual/Mech |

|              | Diffusion<br>Metallization | See Table IV                   |

|              | E-Test                     | Electrical Characteristics     |

Fig. 6. General wafer fabrication flow (continued)

| Process Flow | Process Step                    | Major Control Item                                                                                                                              |

|--------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Back-Lap                        | Thickness                                                                                                                                       |

|              | Back Side Evaporation           | Thickness, Time, Resistivity     Evaporation Rate                                                                                               |

|              | Final Inspection                | All Wafers Screened     (Visual/Mech)                                                                                                           |

|              | QC Fab Final Gate               | • Visual/Mech. AQL 4.0%                                                                                                                         |

|              | EDS<br>(Electrical Die Sorting) |                                                                                                                                                 |

|              | QC Monitor                      | <ul> <li>Function Monitor</li> <li>Ink Dot Size</li> <li>Height of Probe Tip</li> <li>Operability of Probe Tip</li> <li>Misalignment</li> </ul> |

|              | Sawing                          |                                                                                                                                                 |

|              | QC Monitor                      | <ul> <li>Sawing Depth</li> <li>D.I. Water Purity</li> <li>Bacterial Count</li> <li>CO<sub>2</sub> Bubbler Purity</li> <li>Visual</li> </ul>     |

|              | Inspection                      | Die Screen                                                                                                                                      |

|              | QC 2' nd Optical                | <ul> <li>AQL 1.0%</li> <li>Fab Defect</li> <li>Test Defect</li> <li>Sawing Defect</li> </ul>                                                    |

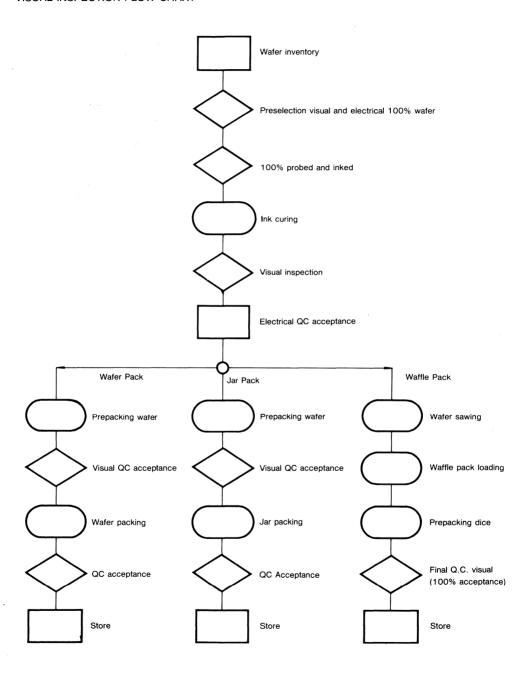

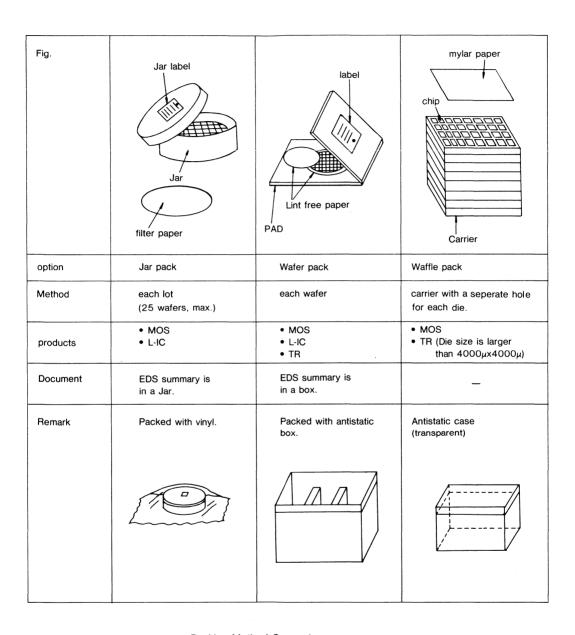

### 3.6.4.5 Shipping procedure for uncapsulated chips

### 3.6.4.5.1 Packing option

There are three kind of packing forms.

#### Waffle pack

This is a 2×2 waffle type carrier with a seperate hole for each die.

Chips are 100% visually inspected with the rejects removed.

#### Wafer pack

The pack contains a wafer that is 100% electrically tested.

With the rejects inked, the wafers is left unsawed and packaged with protective cardboard in a vacuum sealed plastic bag.

### Jar pack

The pack contains 25 wafers(Max.) that are 100% electrically tested.

With the rejects inked, wafers are left unsawed and packaged with protective Jar.

Each wafers are seperated by filter paper.

### 3.6.4.5.2 Visual Inspection

All dies go through extensive visual inspection during die processing. (See flow chart) Dies are inspected at 50X to 100X magnification using SAMSUNG's standard visual inspection criteria which is based on MIL-STD 883C.

Copies of the visual inspection documents are available upon request.

#### Visual Lot Inspection Gates

| Step                                      | Basic<br>Magnification | Production Inspection<br>Volume | QC Inspection<br>Gate |

|-------------------------------------------|------------------------|---------------------------------|-----------------------|

| Fab inprocess                             | 200 X                  | All wafers                      | All lots              |

| Fab outgoing                              | 100 X                  | All wafers                      | All lots              |

| Die visual after sawing<br>(2'nd optical) | 50~100 X               | All chips(100%)                 | All lots              |

Line operators also perform a variety of visual inspection monitors of the quality of their Fab and sawing process and product.

The disposition of material failing visual lot inspection gates is 100 percent rescreening (Wafer/Chip).

Visual Inspection monitor issues are tracked by an ITR (Inspection Trouble Report) system, which prescribes suitable corrective actions.

Defect levels in each visual gate are tracked and reported on a weekly or monthly basis causes of specific defects are identified and resolved.

### 3.6.4.5.3 Storage and handling precautions

It is recommended that all SAMSUNG die be stored at room temperature in an inert environment after removal of the seal from the original shipping package. Special Electro-static Discharge(ESD) precautions should be taken to avoid damage the chips.

SAMSUNG recommends storage in the original ESD shipping package.

Extreme care must be required in handling unencapsulated semiconductors to avoid damage to the chip surface.

The following precautions apply.

#### Waffle pack

Lid and anti-static mylar should be removed slowly and extreme care to avoid disturbing position of the die.

Dies should be handled with smooth tipped vacuum wand only.

Do not use tweezers.

### Wafer pack/Jar pack

Wafer should only be handled near edge with round-ended stainless steel or teflon tweezers. SAMSUNG recommend to use the finger-cot.

### VISUAL INSPECTION FLOW CHART

Packing Method Comparison

### 3.7 Process Control—Assembly

- 3.7.1 Process control and inspection points of the assembly operation are explained and listed below.

- 1) Die inspection

Following 100% inspection by manufacturing, in-process quality control samples each lot according to internal or customer specifications and standards.

2) Die attach inspection

Visual inspection of samples is done periodically on a machine/operator basis. Die attach techniques are monitored and temperatures are verified.

3) Die shear strength

Following die attach, die shear strength testing is performed periodically on a machine/operator basis. Either manual or automatic die shear stressing is used.

4) Wire bond inspection

Visual inspection of samples is complemented by a wire pull test performed periodically during each shift. These checks are also done on a Machine/Operator Basis, and  $\overline{X}R$  data is derived.

5) Pre-Seal/Pre-Encapsulation inspection

Following 100% inspection of each lot, samples are taken on a lot acceptance basis and are inspected according to internal or customer criteria.

6) Seal inspection

Periodic monitoring of the sealing operation checks critical temperature profiles of the sealing oven for both glass and metal seals.

7) Post-seal inspection

Subsequent to a 100% visual inspection, in-process quality control samples each lot for conformance to visual criteria

8) General assembly flow is shown in Fig. 7.

#### 3.7.2 Sampling plans

- Sampling plans are based on an AQL(acceptable quality level) concept, and are determined by internal or customer specifications.

- Raw material incoming inspection See Table V.

Table V Raw material inspections

| Material                | Inspection Item                                                                                          | Acceptable Quality Level                                                                   |  |

|-------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| Lead Frame              | Visual Inspection     Dimension Inspection     Function Test     Work Test                               | LTPD 10%,C=2<br>LTPD 20%, C=0<br>LTPD 20%, C=0<br>LTPD 20%, C=0                            |  |

| Wafer                   | 1) Visual Inspection                                                                                     | AQL 0.65 %                                                                                 |  |

| Au/Al<br>(Wire)         | Visual Inspection     Bond Pull Strength Test     Bondability Test     Chemical Composition Analysis     | LTPD 20%, C=0<br>LTPD 15%, C=2<br>LTPD 1.5%, C=6<br>N=4, C=0                               |  |

| Molding Compound        | Visual Inspection     Moldability Test  3) Chemical Composition Analysis                                 | N=5, C=0<br>Critical Defect: 0.15%<br>Major Defect: 1.0%<br>Minor Defect: 1.5%<br>N=5, C=0 |  |

| Packing Tube<br>& Pins  | Visual Inspection     Dimension Inspection     Electro-Static Inspection     Function Test               | N=20, C=1<br>N=10, C=0<br>N=10, C=0<br>N=10, C=0                                           |  |

| Solder                  | Visual Inspection     Weight Inspection     Chemical Composition Analysis                                | AQL 1.0<br>LTPD 20%, C=0<br>LTPD 20%, C=0                                                  |  |

| Flux                    | Acidity Test     Specific Gravity Test     Chemical Composition Analysis                                 | LTPD 20%, C=0<br>LTPD 20%, C=0<br>LTPD 20%, C=0                                            |  |

| Solder Preform          | Visual Inspection     Work Test     Chemical Composition Analysis                                        | AQL 2.5%<br>AQL 2.5%<br>AQL 2.5%                                                           |  |

| Coating Resin           | Visual Inspection     Work Test     Chemical Composition Analysis                                        | AQL 0.65%<br>AQL 0.65%<br>AQL 0.65%                                                        |  |

| Marking Ink             | 1) Work Test Major Defect: 1.0% Minor Defect: 1.5% 2) Mark Permanency Test                               | Critical Defect: 0.15%  N=5, C=0                                                           |  |

| Chip Carrier            | Visual Inspection     Dimension Inspection     Electro-Static Inspection     Hardness Test     Work Test | AQL 2.5<br>AQL 0.65<br>N=10, C=0<br>N=5, C=0<br>AQL 0.65                                   |  |

| Vinyl Pack              | Visual Inspection     Work Test     Electo-Static Inspection                                             | LTPD 20%, C=0<br>LTPD 20%, C=0<br>LTPD 15%, C=0                                            |  |

| Ag Epoxy                | Work Test     Chemical Composition Analysis                                                              | N=8, C=0<br>N=8, C=0                                                                       |  |

| Letter Marking          | Visual Inspection     Work Test                                                                          | All Inspection                                                                             |  |

| Spare Parts<br>& Others | Dimension Inspection     Visual Inspection                                                               | N=5, C=0<br>N=5, C=0                                                                       |  |

Molding Compound Incoming Inspection Results TA(DUPONT 9900), EDXRF(LINK XR-500)

- 3) In-Process Quality Inspection

- A. Assembly lot acceptance inspection

- (1) Acceptance quality level for wire bond gate inspection

| Defect Class    | Inspection Level | Defect It                                                                                                                            | Items                                                                                                                                      |  |

|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| Critical Defect | AQL 0.65%        | - Missing Metal - Chip Crack - No Probe - Epoxy on Die - Mixed Device - Wrong Bond - Missing Bond                                    | <ul> <li>Diffusion Deffect</li> <li>Ink Die</li> <li>Exposed Contact</li> <li>Bond Short</li> <li>Die Lift</li> <li>Broken Wire</li> </ul> |  |

| Major Defect    | AQL 1.0%         | - Metal Missing  - Metal Adhesion  - Pad Metal(Discolored)  - Tilted Die  - Die Orientation  - Partial Bond                          | <ul><li>Oxide Defect</li><li>Probe Damage</li><li>Metal Corrosion</li><li>Incomplete Wet</li><li>Weakened Wire</li></ul>                   |  |

| Minor Defect    | AQL 1.5%         | <ul> <li>Adjacent Die</li> <li>Passivation Glass</li> <li>Die Attach Defect</li> <li>Wire Loop Height</li> <li>Extra Wire</li> </ul> | <ul><li>Contamination</li><li>Ball Size</li><li>Wire Clearance</li><li>Bond Deformation</li></ul>                                          |  |

## (2) Acceptance quality level for mold/trim gate inspection

| Defect Class    | Inspection Level | Defect Items                                                                            |                                                                                    |  |

|-----------------|------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| Critical Defect | AQL 0.04%        | <ul><li>Incomplete Mold</li><li>Void, Broken Package</li><li>Misalignment</li></ul>     | <ul><li>Deformation</li><li>No Plating</li><li>Broken lead</li></ul>               |  |

| Major Defect    | AQL 0.25%        | <ul><li>Ejector Pin Defect</li><li>Package Burr</li><li>Flash on Lead</li></ul>         | <ul> <li>Crack, Lead Burr</li> <li>Rough Surface</li> <li>Squashed Lead</li> </ul> |  |

| Minor Defect    | AQL 0.40%        | <ul><li>Lead Contamination</li><li>Poor Plating</li><li>Package Contamination</li></ul> | - Bent Lead                                                                        |  |

## B. In-process monitor inspection

| Inspection Item                                                        | Frequency                               | Reference                       |

|------------------------------------------------------------------------|-----------------------------------------|---------------------------------|

| Die Shear Test                                                         | Each Lot                                | MIL-STD-883C, 2019              |

| <ul> <li>Bond Strength Test</li> </ul>                                 | 1 Time/Shift/Each Equip                 | MIL-STD-883C, 2011              |

| <ul> <li>Solderability Test</li> </ul>                                 | Weekly                                  | MIL-STD-883C, 2003              |

| <ul> <li>Mark Permanency Test</li> </ul>                               | Weekly                                  | MIL-STD-883C, 2015              |

| Lead Integrity Test                                                    | Weekly                                  | MIL-STD-883C, 2004              |

| <ul> <li>In-Process Monitor</li> <li>Inspection for Product</li> </ul> | 1 Time/Shift/Each Process               | Verify Relative to Control Unit |

| <ul> <li>X-Ray Monitor</li> <li>Inspection for Molding</li> </ul>      | 1 Time/Shift/Mold Press                 | Verify Relative to Control Unit |

| Monitor Inspection for<br>Production Equipment                         | 2 Times/Shift/Each Unit of<br>Equipment | Verify Relative to Control Unit |

X-Ray Monitor Results (Model: MG161, PHIL1PS)

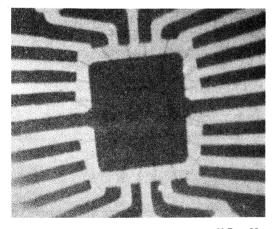

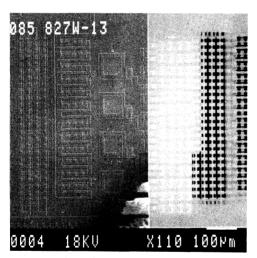

WIRE BONDING MONITOR BY SEM (MODEL JSM IC-845, JEOL)

**APPLICATION OF SEM**

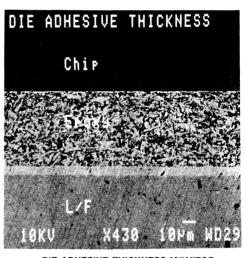

DIE ADHESIVE THICKNESS MONITOR

## 4) Outgoing quality inspection plan(LTPD)

| Defe     | Defect Class         |      | LSI | Kind of Defect                                                                        |  |

|----------|----------------------|------|-----|---------------------------------------------------------------------------------------|--|

| Critical | Electrical<br>Visual | 1%   | 2%  | Open, Short, Wrong Configuration<br>No Marking                                        |  |

| Major    | Electrical<br>Visual | 1.5% | 3%  | Items which affect reliability most strongly                                          |  |

| Minor    | Elec<br>Visual       | 2%   | 5%  | Items which minimally or do not affect reliability at all (Cosmetic, Appearance, Etc) |  |

Fig. 7. General assembly flow

| Process Flow                                                                                                                            | Process Step                  | M                                                                   | lajor Control Item                                                                                  |          |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------|

| $\nabla$                                                                                                                                | Wafer                         |                                                                     |                                                                                                     |          |

|                                                                                                                                         | Wafer Incoming<br>Inspection  | Q.C Wafer I                                                         | ncoming Inspection,                                                                                 | AQL 4.0% |

| ( )                                                                                                                                     | Tape Mount                    |                                                                     |                                                                                                     |          |

|                                                                                                                                         | Sawing Q.C. Monitor           | Q.C Monitoring  - Chip-Out  - Crack  - Sawing Spee  - D.I. Water po | <ul><li>Scratch</li><li>Sawing Disc</li></ul>                                                       |          |

|                                                                                                                                         | Visual Inspection             | 100% Screen:  - FAB Defect  - EDS Test De  - Sawing & Sc            | efect                                                                                               |          |

| $\qquad \qquad $ | Q.C. Gate                     | 1st AQL: 1.0%<br>Reinspection AQL: 0.65%                            |                                                                                                     |          |

|                                                                                                                                         | Leadframe                     |                                                                     |                                                                                                     |          |

|                                                                                                                                         | Leadframe Incoming Inspection | Acceptance     Dimension:     Visual & Med                          | me Incoming Inspect<br>Quality Level<br>LTPD 20%, C=0<br>chanical : LTPD 10%<br>fork Test : LTPD 10 | o, C=2   |

|                                                                                                                                         | Die Attach                    |                                                                     |                                                                                                     |          |

|                                                                                                                                         | Q.C. Monitor                  | Q.C. D/A Moni  Bond Force Frequency 1 Sample: 24 Acceptance         | Time / Station / Shi                                                                                | ift      |

|                                                                                                                                         |                               | Defect                                                              | Acceptance                                                                                          | Reject   |

|                                                                                                                                         |                               | Critical                                                            | 0                                                                                                   | 1        |

|                                                                                                                                         |                               | Major                                                               | 1                                                                                                   | 2        |

Fig. 7. General assembly flow (Continued)

| Process Flow   | Process Step                        | Major Control Item                                                                                                                                                                                               |

|----------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Cure                                |                                                                                                                                                                                                                  |

|                | Q.C. Monitor                        | Q.C. Cure Monitor Inspection  1. Control Item  - Temperature  - In/Out Time  2. Frequency  - 1 Time/Shift                                                                                                        |

|                | Au Wire                             |                                                                                                                                                                                                                  |

|                | Bonding Wire<br>Incoming Inspection | Q.C. Wire Incoming Inspection  1. Visual Inspection: LTPD 20%, C=0  2. Bond Pull Strength Test: N=15, C=2  3. Bondability Test LTPD 1.5%, C=6                                                                    |

|                | Wire Bonding                        |                                                                                                                                                                                                                  |

|                | 100% Visual<br>Inspection           |                                                                                                                                                                                                                  |

|                | Q.C. Monitor                        | Q.C. Wire bond Monitor Inspection Frequency: 3 Times/Machine/Shift                                                                                                                                               |

|                | Q.C. Gate                           | Q.C. Acceptance Quality Level  — Critical Defect: AQL 0.65%  — Major Defect: AQL 1.0 %  — Minor Defect: AQL 1.5 %                                                                                                |

|                | Mold Compound                       |                                                                                                                                                                                                                  |

|                | Incoming Inspection                 | Moldability Test  - Critical Defect : AQL 0.15%  - Major Defect : AQL 1.0 %  - Minor Defect : AQL 1.5 %                                                                                                          |

|                | Mold                                |                                                                                                                                                                                                                  |

|                | Q.C. Monitor                        | Q.C. Mold Monitor Inspection  1. In-Process Monitor Inspection  - Frequency: 3 Times/Station/Shift  - Sample: 1 Shot/Time  2. Acceptance Quality Level  - Critical Defect: AQL 0.065%  - Major Defect: AQL 0.25% |

|                | Cure                                |                                                                                                                                                                                                                  |

|                | Q.C. Monitor                        | Q.C. Cure Monitor Inspection  1. Control Item  — Temperature  — In/Out Time  2. Frequency  — 1 Time/Shift                                                                                                        |

| $   \vee \mid$ | Deflash                             |                                                                                                                                                                                                                  |

Fig. 7. General assembly flow (Continued)

| Process Flow | Process Step                                       | Major Control Item                                                                                                                                                                                                                                    |  |  |  |  |

|--------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|              | Q.C. Monitor                                       | <ul> <li>Q.C. Deflash Monitor Inspection</li> <li>1. Control Item</li> <li>Pressure</li> <li>Belt Speed</li> <li>Visual/Mechanical Inspection</li> <li>2. Frequency: 3 Times/ Machine/Shift</li> <li>3. Identify Each Defect Control Limit</li> </ul> |  |  |  |  |

|              | Trim/Bend                                          |                                                                                                                                                                                                                                                       |  |  |  |  |

|              | Q.C. Monitor                                       | Q.C. Trim/Bend Monitor Inspection 1. Visual Inspection. 2. Frequency: 3 Times/Station/Shift                                                                                                                                                           |  |  |  |  |

|              | Solder                                             | 100% Visual Inspection                                                                                                                                                                                                                                |  |  |  |  |

|              | Q.C. Monitor                                       | Q.C. Solder Monitor Inspection  1. Frequency: 3 Times/Station/Shift  2. Criteria  - Critical Defect: AQL 0.65%  - Major Defect: AQL 1.0 %                                                                                                             |  |  |  |  |

|              | Q.C. Gate                                          | Q.C. Mold Gate  - Acceptance Criteria Critical Defect: AQL 0.04% Major Defect: AQL 0.25% Minor Defect: AQL 0.40%                                                                                                                                      |  |  |  |  |

|              | Test                                               | 100% Electrical Test                                                                                                                                                                                                                                  |  |  |  |  |

|              | Q.C. Monitor                                       | Correlation Sample Read Prior to Initial Device Test                                                                                                                                                                                                  |  |  |  |  |

|              | Mark                                               | 100% Visual Inspection                                                                                                                                                                                                                                |  |  |  |  |

|              | PRT Monitoring<br>(Process Reliability<br>Testing) | 1. PRT for LSI  - HOPL (168 HR)  - PCT (48 HR)  - Other (When Applicable)  2. Acceptance Criteria: LTPD 10%                                                                                                                                           |  |  |  |  |

|              | Q.C. Monitor                                       | Q.C. Marking Monitor Inspection  - Frequency: 3 Times/Station/Shift  - Sample: 50 Units/Time  - Acceptance Criteria                                                                                                                                   |  |  |  |  |

|              |                                                    | Defect Acceptance Reject                                                                                                                                                                                                                              |  |  |  |  |

|              |                                                    | CRITICAL/ MAJOR  0 1                                                                                                                                                                                                                                  |  |  |  |  |

|              | Q.C. Gate                                          | Q.C. Final Acceptance Level  - Critical Defect : AQL 0.065%  - Major Defect : AQL 0.40%  - Minor Defect : AQL 0.65%                                                                                                                                   |  |  |  |  |

Fig 7 General assembly flow (continued)

| Process Flow | Process Step | Major Control Item                                                                                                                                                                                                                                                                                                               |

|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Q.A. Gate    | Q.A. Incoming Inspection for LSI  1. Critical Defect  - Electrical Test: LTPD 2% (N=116, C=0)  - Visual Test: LTPD 2% (N=116, C=0)  2. Major Defect  - Electrical Test: LTPD 3% (N=116, C=0)  - Visual Test: LTPD 3% (N=116, C=0)  3. Minor Defect  - Electrical Test: LTPD 5% (N=116, C=2)  - Visual Test: LTPD 5% (N=116, C=2) |

|              | Stock        | Age Control                                                                                                                                                                                                                                                                                                                      |

|              | Q.A. Gate    | Q.A. Outgoing Inspection 1. Quality 2. Customer 3. Packing 4. Sampling Inspection (When Applicable) — Sampling Plan is Same as Incoming Inspection                                                                                                                                                                               |

|              | Shipment     |                                                                                                                                                                                                                                                                                                                                  |

### 3.8 Material Control

#### 3.8.1 General

It is the policy of Samsung to assure conformance of materials to technical requirements. The extent and type of assurance inspection is based upon evidence of the supplier's degree of quality control, as well as the criticality of the material.

### 3.8.2 Policies

Samsung quality control is responsible for five key areas of incoming material quality. They are detailed below.

- 1) Establishing procedures to address material identification and integrity.

- A. Provide adequate inspection and testing methods.

- B. Assure segregation within production operation regarding materials undergoing inspection, uninspected materials, and non-conforming materials.

- C. Provide for identification of approved materials until processing or fabrication obliterates identitiv. The purity grade-electronic grade is used unless another grade is specified in the process specification.

### 2) Incoming inspection

All materials and pieceparts purchased for production, with the exception of chemicals and gases, must pass through incoming inspection. There they are tested according to the appropriate purchase or incoming inspection specification. As it is not possible to determine the quality of certain items by normal inspection techniques, sometimes additional manufacturing tests are undertaken, which are monitored by quality control. Batch control is maintained when necessary, and the quality is monitored where possible via in-line checks of production processes. The quality department retains the right to carry out acceptance tests on chemicals, but its policy is not to analyze incoming chemical materials as a general practice.

### 3) Rejection/Waiver

When a batch of materials or piece parts fails to meet the incoming inspection specification, it is the responsibility of the incoming inspection group to inform production control, engineering, purchasing and the QC manager of the failure. This is done via distributed documentation. The detailed report provides data for QC and process engineering to assess the criticality of the fault, and its probable effects on quality, yield and cost. If a waiver to accept nonconforming material is considered, a request is initiated by production control, who must obtain the approval of the process engineer, quality control engineer and operating superintendant. In the event of any disagreement at this level, final disposition is by consensus of the quality and manufacturing managers.

#### 4) Non-conforming items

All incoming material is held in quarantine in the incoming inspection section until it is accepted and placed in storage, or rejected and sent out of the factory. Only approved and accepted piece parts and materials are allowed to reach the warehouse.

#### 5) Issue from warehouse

Every consignment in the warehouse bears an incoming lot number, which can be used to refer to an incoming inspection report. Issuance of all batches is in chronological order.

### 3.9 Vendor Relations

It is company policy to encourage cooperation between suppliers and Samsung to achieve high quality at low cost. This is implemented via the methods discussed below.

- 3.9.1 All purchases of production material and pieceparts are made to formal specifications. These specifications specify requirements and give the supplier full details of incoming inspections and AQL's.

- 3.9.2 When a new supplier is approached where critical pieceparts are concerned, or a new requirement arises, the specification is discussed with the supplier to ensure that the specification is understood and attainable.

- 3.9.3 All incoming batches of production material are examined on receipt, and the results of incoming inspections are reported back to the supplier. This is done in the event of batch rejection, observed but non-rejectable faults, and in other cases where feedback of information is considered as necessary.

- 3.9.4 Visits are made to supplier premises whenever it is deemed appropriate to ensure quality.

- 3.9.5 It is company policy to encourage suppliers to institute quality improvements and cost reductions in cooperation with Samsung.

#### 3.10 Control of Finished Product

3.10.1 The company approach to the control of finished devices is that the production department make and completely test all devices. Product is then directed in batches to the quality final acceptance group, who decide on the basis of a predetermined sample plan whether the product is fit for sale. Although a waiver can be issued at this late stage in the case of standard commercial product, it is Samsung's policy that such waivers are given only under very exceptional circumstances. Full details of any such waiver are recorded, and the waiver itself can only be given with the approval of both the quality manager and the marketing manager.

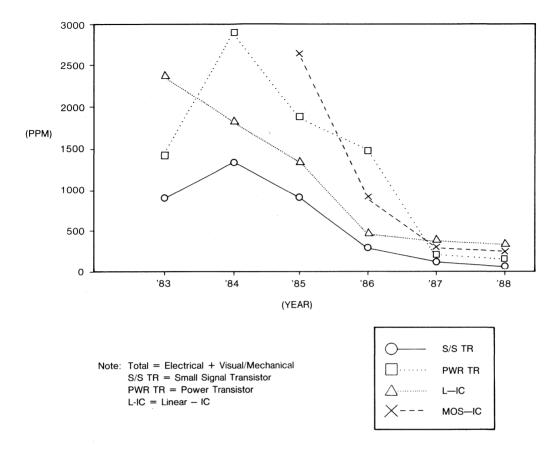

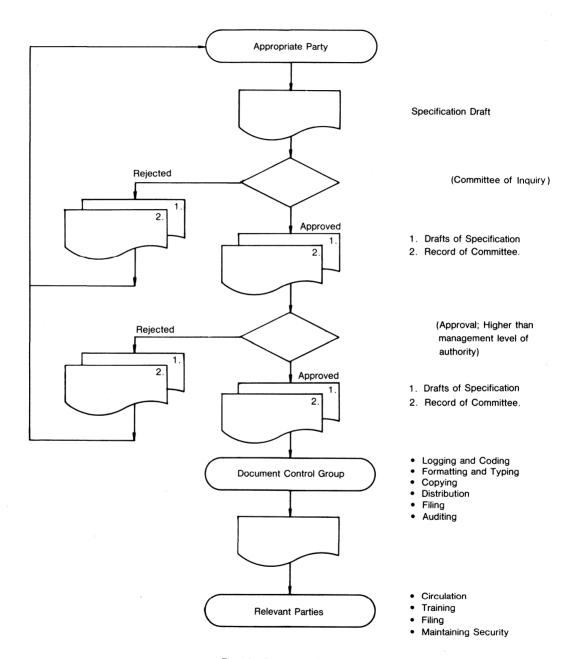

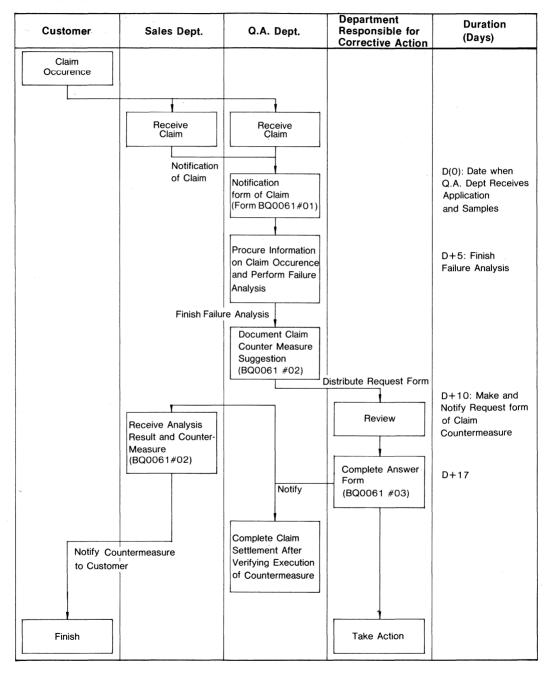

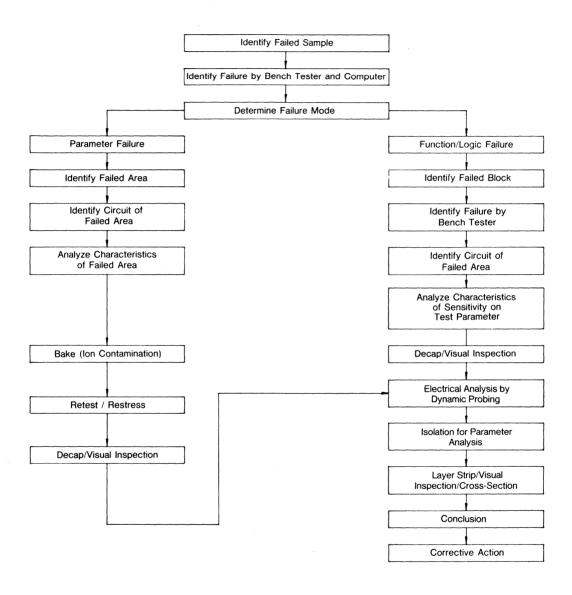

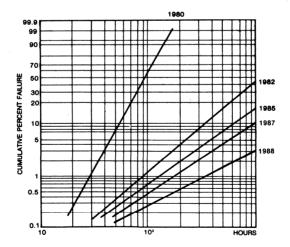

### 3.10.2 Finished goods procedure